Create

Design Project Gallery

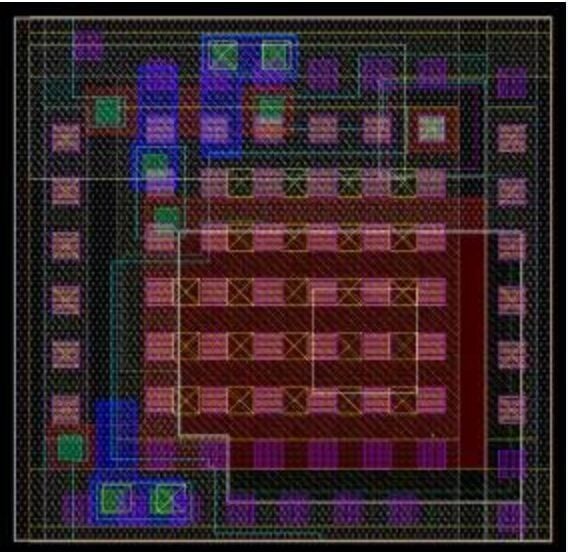

CMOS Imager

- Program: Electrical and Computer Engineering

- Course: EN.520.216 Introduction to VLSI

- Year: 2025

Project Description:

Our project implements a CMOS active-pixel sensor (APS) imager using a 3T pixel architecture. We designed and simulated individual pixel circuits, 4-stage C2MOS-based row and column shift registers, and a column read-out current source with selection switch, all matching pixel pitch. A 4-pixel column is being integrated and simulated to demonstrate sequential readout controlled by shift registers using a shared clock. We expand to a 4×4 APS array with per-column read-out and a second shift register-driven multiplexer for single-pin output. All circuits were designed, simulated for functionality, and laid out in a 2.5mm × 2.5mm area. Scanning of the full array was demonstrated with transient simulation with varied photocurrent values. This project showcases complete schematic, layout, and simulation flow for a functional CMOS imager.